Verilog code for an 8-bit shift-left register with a positive-edge clock, serial in and serial out.

Verilog code for an 8-bit shift-left register with a negative-edge clock, a clock enable, a serial in and a serial out.

Verilog code for an 8-bit shift-left register with a positive-edge clock, asynchronous clear, serial in and serial out.

Verilog code for an 8-bit shift-left register with a positive-edge clock, a synchronous set, a serial in and a serial out.

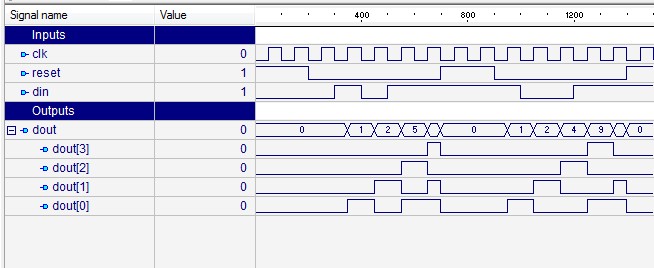

Verilog code for an 8-bit shift-left register with a positive-edge clock, a serial in and a parallel out.

Verilog code for an 8-bit shift-left register with a positive-edge clock, an asynchronous parallel load, a serial in and a serial out.

Verilog code for an 8-bit shift-left register with a positive-edge clock, a synchronous parallel load, a serial in and a serial out.

Verilog code for an 8-bit shift-left/shift-right register with a positive-edge clock, a serial in and a serial out.

- The 74LV165 is an 8-bit parallel-load or serial-in shift register with complementary serial outputs (Q7 and Q7) available from the last stage.When the parallel-load input (PL) is LOW, parallel data from the inputs D0 to D7 are loaded into the register asynchronously.When input PL is HIGH, data enters the register serially at the input DS. It shifts one place to the right (Q0→Q1→Q2, etc.

- At each clock cycle, the content of the register shifts to the right and sin enters into the leftmost bit or the MSB bit. The whole design also has and output that we are c calling sout. At each clock cyccle the right most bit of the register comes out. The picture shows the scheme of the shift register. Here is the verilog implemmentation of.

Shift In Verilog

Verilog Code For IC74LS165 8-Bit Parallel In/Serial Output Shift Registers-適用於DE2-70.